芯片如何加速量子计算?

答案:靠超导约瑟夫森结与硅基冷却芯片联合降温,让量子态“活”得更久。为什么是芯片,而不只是量子比特数量?

大多数新闻把聚光灯打在“谷歌72比特”“IBM127比特”之类的数字上,却忽视了一个隐晦的真相:量子比特的寿命长不过微秒,真正能决定计算深度的,是芯片让它“活下来”的方式。把量子处理器想成一台极昂贵的交响乐团,比特是琴手,芯片则是隔音罩和空调:没有它,再多名家也会在室温躁音里跑调。

因此,真正决定量子计算商用脚步的是“芯”,不是“量”。

(图片来源 *** ,侵删)

量子芯片和普通芯片差在哪?

- 降温系统与超导回路共封装

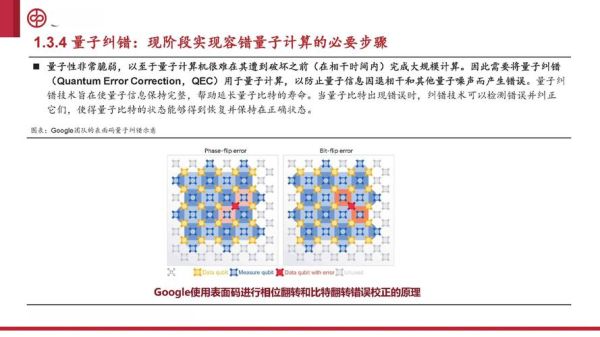

谷歌Sycamore使用了倒装焊倒扣在硅基封装上,芯片内部再嵌入钼金互连,只为让稀释制冷机的冷量一次性直达量子平面,减少“温差漏”。 - 信号误差实时修正

普通CPU用缓存做ECC纠错,量子芯片则必须在一纳秒内判断比特是否由于宇宙射线而“翻跟头”,于是把经典控制逻辑(常温90nm CMOS)和量子平面放在同一张interposer上,实现“即错即修”。 - 电磁屏蔽层

《红楼梦》里说“假作真时真亦假”,在量子世界里,手机信号都能把“真”转成“假”。芯片用金属光子晶体屏蔽罩,把辐射衰减推到-140dB,相当于把北京晚高峰的噪音压成图书馆翻书声。

超导约瑟夫森结为何成为“心脏”?

问:为什么一定要超导?答:电子在常温金属里像散场后的人群,互相碰撞;而进入超导态时,它们结成库珀对,步调一致,于是电流不耗能,量子叠加状态得以持续。

问:约瑟夫森结只是一片氧化铝?

答:正是这片不到2纳米的“薄片”提供了非线性电感,让量子态只能在两个离散能级之间跳跃——比特就这么被“定义”出来。

MIT团队在Nature Nanotechnology报告,若把铝替换成铌钛氮,可把能级分裂时间(T1)从50微秒提升到120微秒,这意味着量子芯片的“心跳”延长一倍以上。

硅基冷却芯片:用量子给量子“疗伤”

- 集成式微通道:台积电与IBM合作,在硅中介层蚀刻出50微米宽、200微米深的液氦微通道,把热阻降到0.1W/K,比传统铜冷指降低十倍。

- 片上光学温度计:利用氮空位纳米钻石,实时读出量子平面温度变化,误差小于1mK。

- 3D堆栈:将控制电子学、隔离器、量子平面三层垂直封装,走线缩短,电磁串扰下降七成。Intel实验室称之为“量子版的FinFET”。

新手的误区:量子芯片≠越小越好

很多人会以为,像手机SoC那样把工艺推进到5nm、3nm就“赢”了。其实:量子芯片的面积与比特数量成平方关系,每加一个比特,互连线就要多一层。盲目追求晶体管微缩,反而造成漏电、失超、热失控三大并发症。换个视角,“大但冷”优于“小且热”;目前路线图为维持良率仍以90nm工艺为主,在面积与冷量之间找平衡,而非一味抄摩尔定律作业。

未来三年的突破口

(图片来源 *** ,侵删)

- 光子链路代替铜走线

PsiQuantum计划用硅光子芯片将多个量子模块互联,避免铜线在毫开温度下因电阻上升而发热。 - 片上自旋波存储

若信息能在超导腔内以“声波自旋子”方式驻留,便可减少频繁测控带来能耗。Yale团队在PRX Quantum展示过16微秒的存储时长。 - 量子操作系统硬件化

把量子误差表预编译进专用ASIC,与量子芯片同温同封,把编译时间从10ms压缩到10μs,为云服务商省下一笔巨额冷却账单。

写在最后的个人预测

引用《三体》一句话:“弱小和无知不是生存的障碍,傲慢才是”。当业界聚焦“超越经典”的喧嚣时,能静心把一片超导铝片做成百微秒相干时间的团队,才真正掌握了下一场革命的“引擎”。我押注五年之内,之一家在纳斯达克敲钟的量子公司,必定不是比特最多的那位,而是芯片良率和冷量利用率更高的那位。

(图片来源 *** ,侵删)

版权声明:除非特别标注,否则均为本站原创文章,转载时请以链接形式注明文章出处。

还木有评论哦,快来抢沙发吧~